# 8 Gb, 4-Bit ECC, x8 I/O and 1.8 V $V_{CC}$ NAND Flash Memory for Embedded

#### **Distinctive Characteristics**

- Density

- -8 Gb (4 Gb x 2)

- Architecture (For each 4 Gb device)

- Input / Output Bus Width: 8-bits

- Page Size: (2048 + 128) bytes; 128-byte spare area

- Block Size: 64 Pages or (128k + 8k) bytes

- Plane Size

- 2048 Blocks per Plane or (256M + 16M) bytes

- Device Size

- 2 Planes per Device or 512 Mbyte

- NAND Flash Interface

- Open NAND Flash Interface (ONFI) 1.0 compliant

- Address, Data and Commands multiplexed

- Supply Voltage

- -1.8V device:  $V_{CC} = 1.7V \sim 1.95V$

- Security

- One Time Programmable (OTP) area

- Serial number (unique ID)

- Hardware program/erase disabled during power transition

- Additional Features

- Supports Multiplane Program and Erase commands

- Supports Copy Back Program

- Supports Multiplane Copy Back Program

- Supports Read Cache

- Electronic Signature

- Manufacturer ID: 01h

- Operating Temperature

- Industrial: -40 °C to 85 °C

- Industrial Plus: -40 °C to 105 °C

#### **Performance**

- Page Read / Program

- Random access: 30 µs (Max)

- Sequential access: 45 ns (Min)

- Program time / Multiplane Program time: 300 μs (Typ)

- Block Erase / Multiplane Erase

- Block Erase time: 3.5 ms (Typ)

- Reliability

- 100,000 Program / Erase cycles (Typ) (with 4-bit ECC per 528 bytes)

- 10 Year Data retention (Typ)

- Blocks zero and one are valid and will be valid for at least 1000

- program-erase cycles with ECC

- Package Options

- Lead Free and Low Halogen

- -63-Ball BGA 9 x 11 x 1 mm

## **Contents**

| 1.  | General Description        | 3  |

|-----|----------------------------|----|

| 2.  | Connection Diagram         | 3  |

| 3.  | Pin Description            | 4  |

| 4.  | Block Diagrams             | 5  |

| 5.  | Addressing                 | 6  |

| 6.  | Read Status Enhanced       | 7  |

|     | Read IDRead Parameter Page |    |

| 8.  | Electrical Characteristics | 12 |

|     | Valid Blocks               |    |

| 8.2 | DC Characteristics         | 12 |

| g 3 | Pin Canacitance            | 13 |

| 8.4 | for Allowed Stacking Configurations  | 13 |

|-----|--------------------------------------|----|

|     | Physical InterfacePhysical Diagram   |    |

| 10. | Ordering Information                 | 15 |

| 11. | Revision History                     | 16 |

| Doc | ument History Page                   | 16 |

|     | es, Solutions, and Legal Information |    |

|     | Worldwide Sales and Design Support   | 17 |

|     | Products                             | 17 |

|     | PSoC® Solutions                      | 17 |

|     | Cypress Developer Community          | 17 |

|     | Technical Support                    | 17 |

## 1. General Description

The Cypress® S34MS08G2 8-Gb NAND is offered in  $1.8V_{CC}$  with x8 I/O interface. This document contains information for the S34MS08G2 device, which is a dual-die stack of two S34MS04G2 die. For detailed specifications, please refer to the discrete die data sheet: S34MS01G2\_04G2.

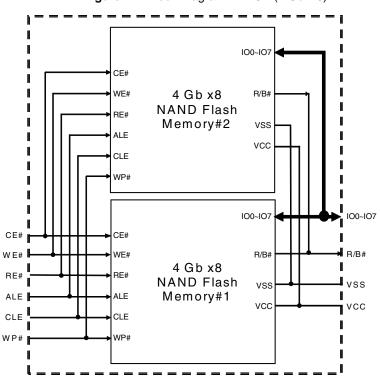

## 2. Connection Diagram

Figure 2.1 63-BGA Contact, x8 Device, Single CE (Top View)

#### Note:

<sup>1.</sup> These pins should be connected to power supply or ground (as designated) following the ONFI specification, however they might not be bonded internally.

## 3. Pin Description

Table 3.1 Pin Description

| Pin Name    | Description                                                                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1/00 - 1/07 | Inputs/Outputs. The I/O pins are used for command input, address input, data input, and data output. The I/O pins float to High-Z when the device is deselected or the outputs are disabled.                                                       |

| CLE         | <b>Command Latch Enable.</b> This input activates the latching of the I/O inputs inside the Command Register on the rising edge of Write Enable (WE#).                                                                                             |

| ALE         | <b>Address Latch Enable.</b> This input activates the latching of the I/O inputs inside the Address Register on the rising edge of Write Enable (WE#).                                                                                             |

| CE#         | <b>Chip Enable.</b> This input controls the selection of the device. When the device is not busy CE# low selects the memory.                                                                                                                       |

| WE#         | <b>Write Enable.</b> This input latches Command, Address and Data. The I/O inputs are latched on the rising edge of WE#.                                                                                                                           |

| RE#         | <b>Read Enable.</b> The RE# input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid t <sub>REA</sub> after the falling edge of RE# which also increments the internal column address counter by one. |

| WP#         | <b>Write Protect.</b> The WP# pin, when low, provides hardware protection against undesired data modification (program / erase).                                                                                                                   |

| R/B#        | Ready Busy. The Ready/Busy output is an Open Drain pin that signals the state of the memory.                                                                                                                                                       |

| VCC         | <b>Supply Voltage</b> . The $V_{CC}$ supplies the power for all the operations (Read, Program, Erase). An internal lock circuit prevents the insertion of Commands when $V_{CC}$ is less than $V_{LKO}$ .                                          |

| VSS         | Ground.                                                                                                                                                                                                                                            |

| NC          | Not Connected.                                                                                                                                                                                                                                     |

#### Notes:

Document Number: 002-00515 Rev. \*E

A 0.1 μF capacitor should be connected between the V<sub>CC</sub> Supply Voltage pin and the V<sub>SS</sub> Ground pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations.

<sup>2.</sup> An internal voltage detector disables all functions whenever V<sub>CC</sub> is below 1.1V to protect the device from any involuntary program/erase during power transitions.

## 4. Block Diagrams

Address Register/ Counter Program Erase Controller HV Generation 8192 Mbit + 512 Mbit (8 Gb Device) DECODER NAND Flash ALE Memory Array CLE WE# CE# Command Interface Logic WP# RE# Page Buffer Y Decoder Command Register I/O Buffer Data Register I/O0~I/O7

Figure 4.1 Functional Block Diagram — 8 Gb

Figure 4.2 Block Diagram — 1 CE (4 Gb x 8)

## 5. Addressing

Table 5.1 Address Cycle Map

| Bus Cycle            | I/O0      | I/O1       | I/O2       | I/O3       | I/O4      | I/O5      | I/O6       | I/O7      |

|----------------------|-----------|------------|------------|------------|-----------|-----------|------------|-----------|

| 1st / Col. Add. 1    | A0 (CA0)  | A1 (CA1)   | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)   | A7 (CA7)  |

| 2nd / Col. Add. 2    | A8 (CA8)  | A9 (CA9)   | A10 (CA10) | A11 (CA11) | Low       | Low       | Low        | Low       |

| 3rd / Row Add. 1     | A12 (PA0) | A13 (PA1)  | A14 (PA2)  | A15 (PA3)  | A16 (PA4) | A17 (PA5) | A18 (PLA0) | A19 (BA0) |

| 4th / Row Add. 2     | A20 (BA1) | A21 (BA2)  | A22 (BA3)  | A23 (BA4)  | A24 (BA5) | A25 (BA6) | A26 (BA7)  | A27 (BA8) |

| 5th / Row Add. 3 (6) | A28 (BA9) | A29 (BA10) | A30 (BA11) | Low        | Low       | Low       | Low        | Low       |

#### Notes:

- 1. CAx = Column Address bit.

- 2. PAx = Page Address bit.

- 3. PLA0 = Plane Address bit zero.

- 4. BAx = Block Address bit.

- 5. Block address concatenated with page address and plane address = actual page address, also known as the row address.

- 6. A30 for 8 Gb (4 Gb x 2 DDP) (1CE).

For the address bits, the following rules apply:

- A0 A11: column address in the page

- A12 A17: page address in the block

- A18: plane address (for multiplane operations) / block address (for normal operations)

- A19 A30: block address

#### 6. Read Status Enhanced

Read Status Enhanced is used to retrieve the status value for a previous operation in the following cases:

■ In the case of concurrent operations on a multi-die stack.

When two dies are stacked to form a dual-die package (DDP), it is possible to run one operation on the first die, then activate a different operation on the second die, for example: Erase while Read, Read while Program, etc.

■ In the case of multiplane operations in the same die.

#### 7. Read ID

The device contains a product identification mode, initiated by writing 90h to the command register, followed by an address input of 00h.

**Note**: If you want to execute Read Status command (0x70) after Read ID sequence, you should input dummy command (0x00) before Read Status command (0x70).

For the S34MS08G2 device, five read cycles sequentially output the manufacturer code (01h), and the device code and 3rd, 4th, and 5th cycle ID, respectively. The command register remains in Read ID mode until further commands are issued to it.

Table 7.1 Read ID for Supported Configurations

| Density                               | Org | V <sub>CC</sub> | 1st | 2nd | 3rd | 4th | 5th |

|---------------------------------------|-----|-----------------|-----|-----|-----|-----|-----|

| 4 Gb                                  | x8  | 1.8V            | 01h | ACh | 90h | 15h | 56h |

| 8 Gb (4 Gb x 2 –<br>DDP with one CE#) | x8  | 1.8V            | 01h | A3h | D1h | 15h | 5Ah |

CE# WE# tWHR tAR ALF tREA RE# 00h 90h I/Ox 01h D3h D1h 95h 5Ah Read ID Makei Address 1 Device 3rd Cycle 4th Cycle 5th Cycle Command Cycle Code Code

Figure 7.1 Read ID Operation Timing — 8 Gb

5th ID Data

Table 7.2 Read ID Byte 5 Description

|                                               | Description       | 1/07                                          | 1/06 1/05 1/04 | I/O3 I/O2 | I/O1 I/O0 |

|-----------------------------------------------|-------------------|-----------------------------------------------|----------------|-----------|-----------|

|                                               | 1 bit / 512 bytes |                                               |                |           | 0 0       |

| F001I                                         | 2 bit / 512 bytes |                                               |                |           | 0 1       |

| ECC Level                                     | 4 bit / 512 bytes |                                               |                |           | 1 0       |

|                                               | 8 bit / 512 bytes | 000<br>001<br>010<br>011<br>100<br>101<br>110 |                | 11        |           |

|                                               | 1                 |                                               |                | 0 0       |           |

| Dlana Numbar                                  | 2                 |                                               |                | 0 1       |           |

| Plane Number  Plane Size (without spare area) | 4                 |                                               |                | 1 0       |           |

|                                               | 8                 |                                               |                | 1 1       |           |

|                                               | 64 Mb             |                                               | 000            |           |           |

|                                               | 128 Mb            |                                               | 0 0 1          |           |           |

| DI O                                          | 256 Mb            |                                               | 0 1 0          |           |           |

|                                               | 512 Mb            |                                               | 0 1 1          |           |           |

| (without spare area)                          | 1 Gb              |                                               | 100            |           |           |

|                                               | 2 Gb              |                                               | 101            |           |           |

|                                               | 4 Gb              |                                               | 110            |           |           |

| Reserved                                      |                   | 0                                             |                |           |           |

## 7.1 Read Parameter Page

The device supports the ONFI Read Parameter Page operation, initiated by writing ECh to the command register, followed by an address input of 00h. The command register remains in Parameter Page mode until further commands are issued to it. Table 7.3 explains the parameter fields.

**Note:** For 32nm Cypress NAND, for a particular condition, the Read Parameter Page command does not give the correct values. To overcome this issue, the host must issue a Reset command before the Read Parameter Page command. Issuance of Reset before the Read Parameter Page command will provide the correct values and will not output 00h values.

Table 7.3 Parameter Page Description

| Byte  | O/M | Description                                                                                                                                                                                                                                                       | Values                                                                            |

|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|       |     | Revision Information and Features B                                                                                                                                                                                                                               | lock                                                                              |

| 0-3   | М   | Parameter page signature Byte 0: 4Fh, "O" Byte 1: 4Eh, "N" Byte 2: 46h, "F" Byte 3: 49h, "I"                                                                                                                                                                      | 4Fh, 4Eh, 46h, 49h                                                                |

| 4-5   | М   | Revision number  2-15 Reserved (0)  1 1 = supports ONFI version 1.0  0 Reserved (0)                                                                                                                                                                               | 02h, 00h                                                                          |

| 6-7   | М   | Features supported 5-15 Reserved (0) 4 1 = supports odd to even page Copyback 3 1 = supports interleaved operations 2 1 = supports non-sequential page programming 1 1 = supports multiple LUN operations 0 1 = supports 16-bit data bus width                    | 1Eh, 00h                                                                          |

| 8-9   | М   | Optional commands supported 6-15 Reserved (0) 5 1 = supports Read Unique ID 4 1 = supports Copyback 3 1 = supports Read Status Enhanced 2 1 = supports Get Features and Set Features 1 1 = supports Read Cache commands 0 1 = supports Page Cache Program command | 3Bh, 00h                                                                          |

| 10-31 |     | Reserved (0)                                                                                                                                                                                                                                                      | 00h                                                                               |

|       | •   | Manufacturer Information Block                                                                                                                                                                                                                                    |                                                                                   |

| 32-43 | М   | Device manufacturer (12 ASCII characters)                                                                                                                                                                                                                         | 53h, 50h, 41h, 4Eh, 53h, 49h, 4Fh, 4Eh, 20h, 20h, 20h, 20h                        |

| 44-63 | М   | Device model (20 ASCII characters)                                                                                                                                                                                                                                | 53h, 33h, 34h, 4Dh, 53h, 30h, 38h, 47h, 32h, 20h, 20h, 20h, 20h, 20h, 20h, 20h, 2 |

| 64    | М   | JEDEC manufacturer ID                                                                                                                                                                                                                                             | 01h                                                                               |

| 65-66 | 0   | Date code                                                                                                                                                                                                                                                         | 00h                                                                               |

| 67-79 |     | Reserved (0)                                                                                                                                                                                                                                                      | 00h                                                                               |

|       |     | Memory Organization Block                                                                                                                                                                                                                                         |                                                                                   |

| 80-83 | М   | Number of data bytes per page                                                                                                                                                                                                                                     | 00h, 08h, 00h, 00h                                                                |

| 84-85 | М   | Number of spare bytes per page                                                                                                                                                                                                                                    | 80h, 00h                                                                          |

| 86-89 | М   | Number of data bytes per partial page                                                                                                                                                                                                                             | 00h, 00h, 00h, 00h                                                                |

| 90-91 | М   | Number of spare bytes per partial page                                                                                                                                                                                                                            | 00h, 00h                                                                          |

| 92-95 | M   | Number of pages per block                                                                                                                                                                                                                                         | 40h, 00h, 00h, 00h                                                                |

Table 7.3 Parameter Page Description (Continued)

| Byte    | O/M | Description                                                                                                                                                                                                                       | Values             |

|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 96-99   | М   | Number of blocks per logical unit (LUN)                                                                                                                                                                                           | 00h, 20h, 00h, 00h |

| 100     | М   | Number of logical units (LUNs)                                                                                                                                                                                                    | 01h                |

| 101     | М   | Number of address cycles 4-7 Column address cycles 0-3 Row address cycles                                                                                                                                                         | 23h                |

| 102     | М   | Number of bits per cell                                                                                                                                                                                                           | 01h                |

| 103-104 | М   | Bad blocks maximum per LUN                                                                                                                                                                                                        | A3h, 00h           |

| 105-106 | М   | Block endurance                                                                                                                                                                                                                   | 01h, 05h           |

| 107     | М   | Guaranteed valid blocks at beginning of target                                                                                                                                                                                    | 01h                |

| 108-109 | М   | Block endurance for guaranteed valid blocks                                                                                                                                                                                       | 01h, 03h           |

| 110     | М   | Number of programs per page                                                                                                                                                                                                       | 04h                |

| 111     | М   | Partial programming attributes 5-7 Reserved 4 1 = partial page layout is partial page data followed by partial page spare 1-3 Reserved 0 1 = partial page programming has constraints                                             | 00h                |

| 112     | М   | Number of bits ECC correctability                                                                                                                                                                                                 | 04h                |

| 113     | М   | Number of interleaved address bits 4-7 Reserved (0) 0-3 Number of interleaved address bits                                                                                                                                        | 01h                |

| 114     | 0   | Interleaved operation attributes  4-7 Reserved (0)  3 Address restrictions for program cache  2 1 = program cache supported  1 1 = no block address restrictions  0 Overlapped / concurrent interleaving support                  | 04h                |

| 115-127 |     | Reserved (0)                                                                                                                                                                                                                      | 00h                |

|         |     | Electrical Parameters Block                                                                                                                                                                                                       |                    |

| 128     | М   | I/O pin capacitance                                                                                                                                                                                                               | 0Ah                |

| 129-130 | М   | Timing mode support 6-15 Reserved (0) 5 1 = supports timing mode 5 4 1 = supports timing mode 4 3 1 = supports timing mode 3 2 1 = supports timing mode 2 1 1 = supports timing mode 1 0 1 = supports timing mode 0, shall be 1   | 03h, 00h           |

| 131-132 | 0   | Program cache timing mode support 6-15 Reserved (0) 5 1 = supports timing mode 5 4 1 = supports timing mode 4 3 1 = supports timing mode 3 2 1 = supports timing mode 2 1 1 = supports timing mode 1 0 1 = supports timing mode 0 | 03h, 00h           |

| 133-134 | М   | t <sub>PROG</sub> Maximum page program time (μs)                                                                                                                                                                                  | BCh, 02h           |

| 135-136 | М   | t <sub>BERS</sub> Maximum block erase time (µs)                                                                                                                                                                                   | 10h, 27h           |

Table 7.3 Parameter Page Description (Continued)

| Byte    | O/M | Description                                            | Values                      |

|---------|-----|--------------------------------------------------------|-----------------------------|

| 137-138 | М   | t <sub>R</sub> Maximum page read time (μs)             | 1Eh, 00h                    |

| 139-140 | М   | t <sub>CCS</sub> Minimum Change Column setup time (ns) | C8h, 00h                    |

| 141-163 |     | Reserved (0)                                           | 00h                         |

|         |     | Vendor Block                                           |                             |

| 164-165 | М   | Vendor specific Revision number                        | 00h                         |

| 166-253 |     | Vendor specific                                        | 00h                         |

| 254-255 | М   | Integrity CRC                                          | 18h, C2h                    |

|         |     | Redundant Parameter Pages                              |                             |

| 256-511 | М   | Value of bytes 0-255                                   | Repeat Value of bytes 0-255 |

| 512-767 | М   | Value of bytes 0-255                                   | Repeat Value of bytes 0-255 |

| 768+    | 0   | Additional redundant parameter pages                   | FFh                         |

#### Note:

<sup>1. &</sup>quot;O" Stands for Optional, "M" for Mandatory.

## 8. Electrical Characteristics

#### 8.1 Valid Blocks

Table 8.1 Valid Blocks

| Device    | Symbol          | Min      | Тур | Max  | Unit   |

|-----------|-----------------|----------|-----|------|--------|

| S34MS04G2 | $N_{VB}$        | 4016     | _   | 4096 | Blocks |

| S34MS08G2 | N <sub>VB</sub> | 8032 (1) | _   | 8192 | Blocks |

#### Note:

#### 8.2 DC Characteristics

Table 8.2 DC Characteristics and Operating Conditions

| Parame                  | ter              | Symbol                | Test Conditions                                                           | Min                   | Тур | Max                   | Units |

|-------------------------|------------------|-----------------------|---------------------------------------------------------------------------|-----------------------|-----|-----------------------|-------|

| Power On Current        | Power On Current |                       | FFh command input after power on                                          | _                     | _   | 50 per<br>device      | mA    |

|                         | Sequential Read  | I <sub>CC1</sub>      | $t_{RC} = t_{RC} \text{ (min)}$ $CE\# = V_{IL},$ $I_{OUT} = 0 \text{ mA}$ | _                     | 15  | 30                    | mA    |

| Operating Current       | Program          | 1                     | Normal                                                                    | _                     | 15  | 30                    | mA    |

|                         | Flogialli        | I <sub>CC2</sub>      | Cache                                                                     | _                     | 15  | 30                    | mA    |

|                         | Erase            | I <sub>CC3</sub>      | _                                                                         | _                     | 15  | 30                    | mA    |

| Standby Current, (TTL)  |                  | I <sub>CC4</sub>      | $CE# = V_{IH},$ $WP# = 0V/Vcc$                                            | _                     | _   | 1                     | mA    |

| Standby Current, (CMOS) |                  | I <sub>CC5</sub>      | $CE\# = V_{CC}-0.2,$ $WP\# = 0/V_{CC}$                                    | _                     | 10  | 50                    | μΑ    |

| Input Leakage Current   |                  | I <sub>LI</sub>       | $V_{IN} = 0$ to $V_{CC}(max)$                                             | _                     | _   | ±10                   | μΑ    |

| Output Leakage Current  |                  | I <sub>LO</sub>       | $V_{OUT} = 0$ to $V_{CC}(max)$                                            | _                     | _   | ±10                   | μΑ    |

| Input High Voltage      |                  | V <sub>IH</sub>       | _                                                                         | V <sub>CC</sub> x 0.8 | _   | V <sub>CC</sub> + 0.3 | V     |

| Input Low Voltage       |                  | V <sub>IL</sub>       | _                                                                         | -0.3                  | _   | V <sub>CC</sub> x 0.2 | V     |

| Output High Voltage     |                  | V <sub>OH</sub>       | I <sub>OH</sub> = -400 μA                                                 | 2.4                   | _   | _                     | V     |

| Output Low Voltage      |                  | V <sub>OL</sub>       | I <sub>OL</sub> = 2.1 mA                                                  | _                     | _   | 0.4                   | V     |

| Output Low Current (R/B | #)               | I <sub>OL(R/B#)</sub> | V <sub>OL</sub> = 0.4V                                                    | 8                     | 10  | _                     | mA    |

| Erase and Program Lock  | out Voltage      | $V_{LKO}$             | _                                                                         | _                     | 1.1 | _                     | V     |

#### Notes:

- 1. All  $V_{\mbox{\footnotesize{CC}}}$  pins, and  $V_{\mbox{\footnotesize{SS}}}$  pins respectively, are shorted together.

- 2. Values listed in this table refer to the complete voltage range for  $V_{CC}$  and to a single device in case of device stacking.

- 3. All current measurements are performed with a 0.1  $\mu$ F capacitor connected between the  $V_{CC}$  Supply Voltage pin and the  $V_{SS}$  Ground pin.

- 4. Standby current measurement can be performed after the device has completed the initialization process at power up.

<sup>1.</sup> Each 4 Gb has maximum 80 bad blocks.

## 8.3 Pin Capacitance

**Table 8.3** Pin Capacitance (TA = 25°C, f=1.0 MHz)

| Parameter      | Symbol          | Test Condition | Min | Max | Unit |

|----------------|-----------------|----------------|-----|-----|------|

| Input          | C <sub>IN</sub> | $V_{IN} = 0V$  | _   | 10  | pF   |

| Input / Output | C <sub>IO</sub> | $V_{IL} = 0V$  | _   | 10  | pF   |

#### Note:

## 8.4 Power Consumptions and Pin Capacitance for Allowed Stacking Configurations

When multiple dies are stacked in the same package, the power consumption of the stack will increase according to the number of chips. As an example, the standby current is the sum of the standby currents of all the chips, while the active power consumption depends on the number of chips concurrently executing different operations.

When multiple dies are stacked in the same package the pin/ball capacitance for the single input and the single input/output of the combo package must be calculated based on the number of chips sharing that input or that pin/ball.

<sup>1.</sup> For the stacked devices version the Input is 10 pF x [number of stacked chips] and the Input/Output is 10 pF x [number of stacked chips].

## **Physical Interface**

#### **Physical Diagram** 9.1

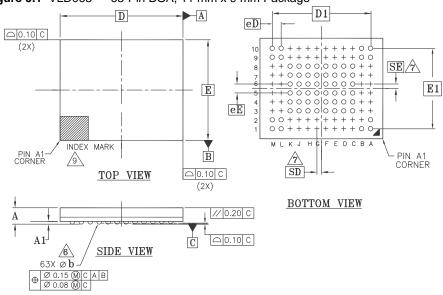

#### 9.1.1 63-Pin Ball Grid Array (BGA)

Figure 9.1 VLD063 — 63-Pin BGA, 11 mm x 9 mm Package

| PACKAGE | VLD 063                                                                                                                                        |           |      |                          |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|--------------------------|--|--|

| JEDEC   | M0-207(M)                                                                                                                                      |           |      |                          |  |  |

|         | 11.00 mm x 9.00 mm<br>PACKAGE                                                                                                                  |           | mm   |                          |  |  |

| SYMBOL  | MIN                                                                                                                                            | NOM       | MAX  | NOTE                     |  |  |

| Α       |                                                                                                                                                |           | 1.00 | PROFILE                  |  |  |

| A1      | 0.25                                                                                                                                           |           |      | BALL HEIGHT              |  |  |

| D       | 11.00 BSC.                                                                                                                                     |           |      | BODY SIZE                |  |  |

| E       | 9.00 BSC.                                                                                                                                      |           |      | BODY SIZE                |  |  |

| D1      | 8.80 BSC.                                                                                                                                      |           |      | MATRIX FOOTPRINT         |  |  |

| E1      | 7.20 BSC.                                                                                                                                      |           |      | MATRIX FOOTPRINT         |  |  |

| MD      | 12                                                                                                                                             |           |      | MATRIX SIZE D DIRECTION  |  |  |

| ME      | 10                                                                                                                                             |           |      | MATRIX SIZE E DIRECTION  |  |  |

| n       | 63                                                                                                                                             |           |      | BALL COUNT               |  |  |

| øb      | 0.40                                                                                                                                           | 0.45 0.50 |      | BALL DIAMETER            |  |  |

| еE      | 0.80 BSC.                                                                                                                                      |           |      | BALL PITCH               |  |  |

| eD      | 0:80 BSC.                                                                                                                                      |           |      | BALL PITCH               |  |  |

| SD      | 0.40 BSC.                                                                                                                                      |           |      | SOLDER BALL PLACEMENT    |  |  |

| SE      | 0.40 BSC.                                                                                                                                      |           |      | SOLDER BALL PLACEMENT    |  |  |

|         | A3-A8,B2-B8,C1,C2,C9,C10<br>D1,D2,D9,D10,E1,E2,E9,E10<br>F1,F2,F9,F10,G1,G2,G9,G10<br>H1,H2,H9,H10,J1,J2,J9,J10<br>K1,K2,K9,K10<br>L3-L8,M3-M8 |           |      | DEPOPULATED SOLDER BALLS |  |  |

- DIMENSIONING AND TOLERANCING METHODS PER ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.

- BALL POSITION DESIGNATION PER JEP95, SECTION 3, SPP-020.

- 4. e REPRESENTS THE SOLDER BALL GRID PITCH

- 5. SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D" DIRECTION.

- SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE "E" DIRECTION.

- n IS THE TOTAL NUMBER OF POPULATED SOLDER BALL POSITIONS FOR MATRIX SIZE MD X ME.

- DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL DIAMETER IN A PLANE PARALLEL TO DATUM C.

- "SD" AND "SE" ARE MEASURED WITH RESPECT TO DATUMS

A AND B AND DEFINE THE POSITION OF THE CENTER

SOLDER BALL IN THE OUTER ROW.

- WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW "SD" OR "SE" = 0.

- WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, "SD" = eD/2 AND "SE" = eE/2.

- "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED BALLS.

- A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK MARK, METALLIZED MARK INDENTATION OR OTHER MEANS.

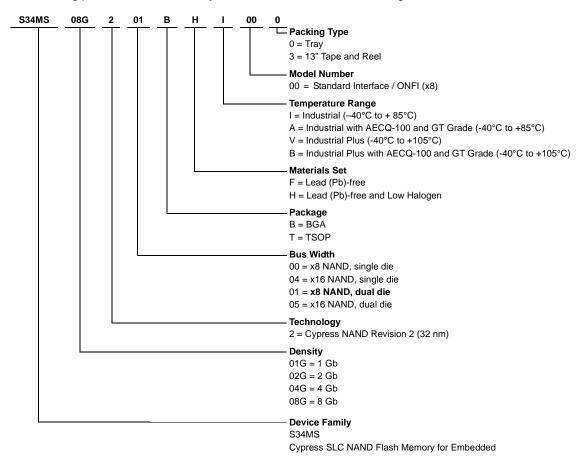

## 10. Ordering Information

The ordering part number is formed by a valid combination of the following:

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific valid combinations and to check on newly released combinations.

| Valid Combinations |         |            |              |                 |                      |                                |                 |                        |

|--------------------|---------|------------|--------------|-----------------|----------------------|--------------------------------|-----------------|------------------------|

| Device<br>Family   | Density | Technology | Bus<br>Width | Package<br>Type | Temperature<br>Range | Additional<br>Ordering Options | Packing<br>Type | Package<br>Description |

| S34MS              | 08G     | 2          | 01           | BH              | I, A, V, B           | 00                             | 0, 3            | BGA                    |

## 11. Revision History

## **Document History Page**

| Rev. | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                          |

|------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | -       | XILA               | 08/04/2014         | Initial release                                                                                                                                                                                                                |

| *A   | _       | XILA               | 09/25/2014         | Read Parameter Page: Parameter Page Description table - updated values for bytes 96-<br>99, 100, 103-104, 254-255                                                                                                              |

| *B   | 4955761 | XILA               | 10/15/2015         | Updated to Cypress template                                                                                                                                                                                                    |

| *C   | 5080707 | XILA               | 01/12/2016         | Added "Industrial Plus" Temperature Range related information in all instances across the document.                                                                                                                            |

| *D   | 5234924 | XILA               | 04/27/2016         | Changed status from Advance to Final. Updated Read ID: Updated Read Parameter Page: Updated description. Updated Ordering Information: Updated definitions for "A" and "B" under "Temperature Range". Updated to new template. |

| *E   | 5497760 | XILA               | 10/27/2016         | Updated Table 8.2. Updated Notes 1 and 2 in Electrical Characteristics. Updated Copyright and Disclaimer.                                                                                                                      |

#### Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Wireless/RF

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot Lighting & Power Control cypress.com/powerpsoc Memory cypress.com/memory **PSoC** cypress.com/psoc **Touch Sensing** cypress.com/touch **USB Controllers** cypress.com/usb

cypress.com/wireless

#### PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2014-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 002-00515 Rev. \*E Revised October 27, 2016 Page 17 of 17